반도체 이야기 5 - 반도체의 8대 공정 3

페이지 정보

작성일 25-02-17 10:15본문

오늘은 반도체 이야기 다섯번째 시간으로 반도체의 8대 공정 중 포토 공정에 대해 알아보도록 하겠다.

반도체의 8대 공정- 3. 포토(Photo Lithography)공정

웨이퍼가 만들어지면 웨이퍼 위에 보호막인 산화막을 만들게 되고, 그 위에 회로를 그려 넣게 된다.

포토 리소그래피(Photo Lithography)를 줄여서 포토공정(Photo)이라고 한다.

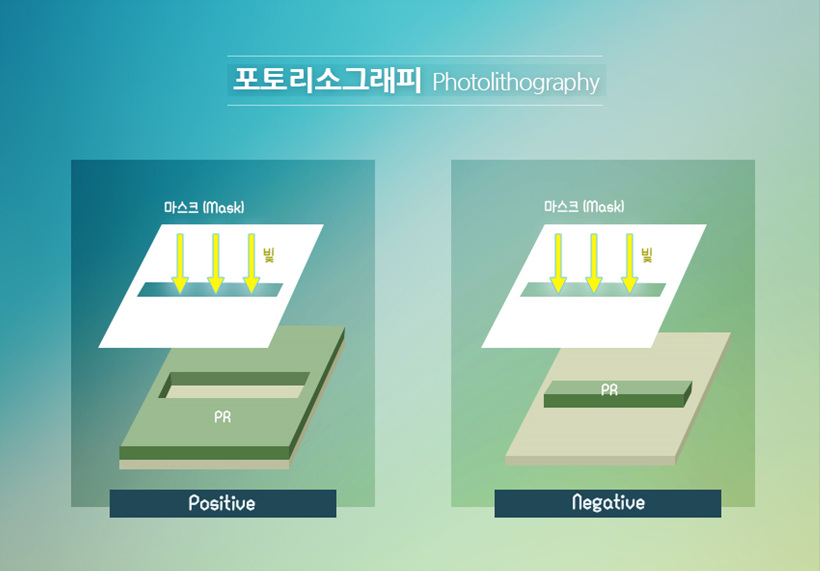

필름 카메라로 찍은 흑백사진을 인화하는 것과 유사한데, 웨이퍼 위에 회로 패턴이 담긴 마스크 상을 빛을 이용하여 회로를 그리기 때문에 붙여진 이름이다.

포토공정의 진행과정은

실리콘 웨이퍼 표면을 깨끗하고, 평탄하게 만드는 것으로부터 시작 된다. 그 후 웨이퍼 표면에 포토레지스트(Photoresist)를 얇게 도포하고, soft bake공정을 통해 포토레지스트를 웨이퍼 표면에 잘 밀착시킨 다음 노광장비를 통해 회로 패턴을 새긴 후 현상(Development)을 통해 포토레지스트를 제거하여 웨이퍼 표면에 패턴이 드러나게 한다.

그 후 에칭(Etching)공정을 통해 웨이퍼를 물리적, 화학적으로 패턴을 형성하고 필요 없는 포토레지스트를 제거함으로써 모든 공정이 완료된다.

포토공정을 수행하기 위해서는 웨이퍼, 감광층, 노광장비, 포토마스크가 필요하다.

필름에 빛에 반응하는 감광제가 발라져 있듯 웨이퍼에도 빛에 반응하는 감광층을 만들어 줘야한다. 감광액을 얇게 바름으로써 감광층을 만들 수 있다.

노광장비는 반도체 제조 공정에서 사용되는 핵심 장비 중 하나이며, 반도체 회로 패턴을 형성하는데 사용된다. 세계적으로 유명한 슈퍼 ’을’ 로 유명한 네덜란드의 ASML이 EUV 기술의 선도 기업으로 독점적인 위치를 차지하고 있다.

노광(Stepper Exposure)은 빛을 이용하여 웨이퍼에 회로를 그려 넣는 공정이다.

노광장비에는 광원(Light Source), 마스크(Reticle), 렌즈(Projection Lens), 스테퍼(Stepper), 스캐너(Scanner)가 있다.

광원(Light Source)의 종류는

고압 수은 아크 램프(G-line - 436nm, H-line - 405nm, I-line - 365nm), KrF 엑시머 레이저(248nm), ArF 엑시머 레이저(193nm), EUV(Extreme UV, 13.5nm) 가 있으며, 위 순서로 발전하였다. EUV는 차세대 공정에서 사용되는 극자외선이다.

Reticle은 회로 패턴을 정착시킬 때 쓰는 원판을 의미하며, 반도체 회로 패턴이 새겨져 있는 유리 재질의 기판이다. 광원이 이 마스크를 통과하며 웨이퍼 위에 패턴을 형성하게 된다.

회로 패턴을 만들 때 마스크의 회로 패턴을 축소하여 웨이퍼에 투사하게 되는데 이때 고해상도의 초정밀 렌즈(Projection Lens)가 사용된다.

회로를 만들기 위해서는 웨이퍼를 정밀하게 이동하는 것이 필요하다. 이때 스테퍼와 스캐너가 필요하다.

스테퍼는 각 패턴을 웨이퍼에 한번씩 노광하며, 스캐너는 움직이면서 패턴을 연속적으로 노광하는 특징을 가진다.

포토공정에서 패턴을 형성하는데 많은 기술들이 있다.

그중, DUV(Deep Ultraviolet)는 193nm 또는 248nm 파장의 빛을 사용하여 패턴을 형성하는 것을 말하며, EUV(Extreme Ultraviolet)는 13.5nm의 극자외선을 이용하여 패턴을 형성하며, 7nm 이하의 공정에서 사용된다.

그리고 단일 노광으로 구현하기 어려운 초미세 패턴을 두번 이상 노광하는 멀티패터닝 기술(Multi-Patterning)기술 또한 상당히 발전하였다.

포토공정은 반도체 제조에서 칩 설계의 물리적 구현을 가능하게 하며, 웨이퍼 상의 회로를 정밀하게 배열하는데 핵심적인 역할을 한다. 반도체 미세화와 성능 개선의 중심에 있는 기술로, 공정에서의 오차를 최소화하기 위해 지속적인 기술 개발이 이루어지고 있다.